2025 INTERNATIONAL CONFERENCE ON COMPUTER-AIDED DESIGN

# CONFERENCE PROGRAM

SPONSORS AND ORGANIZERS

Please visit our website for more information!

2025.ICCAD.COM

# **Table of Contents**

| Executive Committee         | 3   |

|-----------------------------|-----|

| Venue Map & Information     | 4   |

| Welcome Message             | 7   |

| Awards                      | 9   |

| BPA Candidates (Front End)  | 11  |

| BPA Candidates (Back End)   | 13  |

| Plenary Speakers            | 15  |

| Tutorial Sessions           | 18  |

| Workshops                   | 20  |

| Panel Session               | 27  |

| CEDA Luncheon               | 28  |

| Workforce Development       | 29  |

| Social Functions            | 30  |

| Sponsors & Exhibitors       | 31  |

| Program at a Glance         | 33  |

| Technical Program – Oct. 26 | 38  |

| Technical Program – Oct. 27 | 39  |

| Technical Program – Oct. 28 | 67  |

| Technical Program – Oct. 29 | 98  |

| Technical Program – Oct. 30 | 126 |

### **Executive Committee**

#### General Chair

Robert Wille, Technical University of Munich, Munich Quantum Software Company, and Software Competence Center Hagenberg GmbH

#### Past Chair

Jinjun Xiong, University at Buffalo, USA

#### Program Chair

Deming Chen, University of Illinois, USA

### Vice Program Chair

Ismail S. K. Bustany, AMD, USA

### **Tutorial & Special Session Chair**

Tsung-Yi Ho, The Chinese University of Hong Kong, China

### Workshop Chair

Ron Duncan, Synopsys

#### **CEDA Representative**

Jiang Hu, Texas A&M University, USA

### **ACM SIGDA Representative**

Wanli Chang, Hunan University, China

### Asian Representative

Wei Zhang, The Hong Kong University of Science and Technology, China

### **European Representative**

Ulf Schlichtmann, Technical University of Munich, Germany

#### **Industry Liaison**

Haoxing (Mark) Ren, NVIDIA, USA

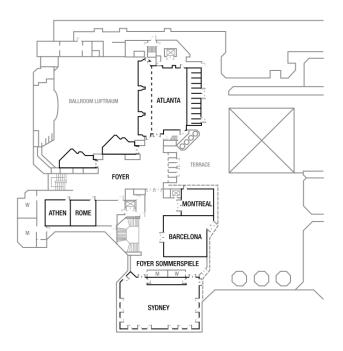

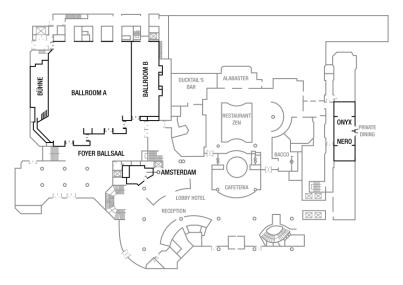

# **Venue Map & Information**

#### The Westin Grand Munich

Address: Arabellastraße 6, 81925 München, Germany

### Parking at the Hotel

On-Site Parking: Hourly: €3.50; Daily: €35.00

### Venue Map

#### MEETING ROOMS

### THE NETWORK!

**Chipdesign Germany** is the leading agile network for chip design in Germany.

### **Chipdesign Germany**

- ... strengthens microelectronics in Germany

- ... connects industry and research

- ... is the think tank for chip design

- ... attracts skilled labour

- ... increases the visibility of chip design

### Contact

info@chipdesign-germany.de www.chipdesign-germany.de

Creating innovations together!

Your expertise counts!

# Venue Map & Info (cont.)

### MEETING ROOMS

# **Welcome Message**

Dear Attendees of ICCAD 2025,

Welcome to Munich, Germany—and welcome to the 44th International Conference on Computer-Aided Design (ICCAD). It is our immense pleasure to host this vibrant community for the next five days and to offer an exciting program filled with opportunities for exchange, networking, and professional growth.

Jointly sponsored by ACM and IEEE, ICCAD **remains the premier venue** for presenting cutting-edge research and exploring emerging technologies in computer-aided

design. From devices and circuits to architectures, systems, as well as applications—especially in the age of AI and heterogeneous computing—ICCAD brings together thought leaders, innovators, and passionate researchers from around the world.

And ICCAD continues to thrive and evolve! For the first time in its over 40-year history, the conference is being held in Europe—marking a major milestone and underscoring ICCAD's transformation into a truly international event. Moreover, for the sixth consecutive year, the number of submissions has increased. Since 2020, ICCAD has more than doubled its submission volume, a testament to the strength, vitality, and expanding reach of the EDA/CAD research community—and a guarantee of an outstanding technical program.

This year, ICCAD has set a new record for paper submissions, with **1508 abstract submissions across 19 technical tracks from 37 regions and countries**. A total of 1078 full papers underwent a rigorous review process, supported by 384 exceptional expert reviewers on our Technical Program Committee. Ultimately, **266 papers were accepted**, resulting in a competitive acceptance rate of 24.7%. These papers are organized into 50 sessions, **forming the largest technical program in ICCAD's history**.

In addition to the regular sessions, we are proud to feature:

- 14 special sessions exploring the future of CAD—including microfluidics, chiplet systems, hardware-software co-design for AI, LLM foundations, neuromorphic computing, and more.

- 2 embedded tutorials on hardware security and quantum architecture design.

- And, for the first time at ICCAD, a panel discussion on the limits and potential of large AI models in hardware design.

Our program is crowned by three **distinguished keynotes** from leaders in the field:

- On Monday morning, Diana Marculescu (University of Texas at Austin) will speak on "The Quest for Energy-Efficient Generative AI."

- On Tuesday morning, Hans-Jörg Vögel (BMW Group) will present "Driven by AI

Driving Requires More Compute Than Ever."

- On Wednesday morning, Luca Benini (Università di Bologna) will share insights on "End-to-End Open Source Platforms in the Era of Domain-Specific Design Automation."

# **Welcome Message (cont.)**

Finally, on Thursday, we invite you to join several **co-located workshops** covering topics such as: Automotive Chiplets, Post-Quantum Cryptography, Top Picks in Hardware & Embedded Security, Sustainable Hardware Security, System Level Interconnect Pathfinding, Quantum Computing Applications & Systems, Foundation Models and EDA. These workshops offer a space for focused discussion and deeper engagement with emerging areas of research.

In addition, throughout the week, ICCAD will also host sessions dedicated to workforce development and student engagement. Our integrated Student Scholar Program supports young researchers through activities such as the SIGDA CADathlon, the ACM Student Research Competition, and the SIGDA Job Fair. Thanks to generous support from our sponsors, we are proud to welcome many first-time attendees and provide travel grants to help students connect with the ICCAD community.

None of this would be possible without the tireless efforts of our volunteers—including the executive committee, technical program committee, workshop organizers, and student activity coordinators. We also want to extend heartfelt thanks to our sponsors for their continued support and belief in ICCAD's mission.

Finally, the success of ICCAD hinges on your participation. We hope you will have a great time, gain new insights, share recent accomplishments, reconnect with old friends, and forge new connections. Whether you're here to present, learn, collaborate, or simply engage with the community—welcome to ICCAD 2025! We hope you enjoy the conference, the city of Munich, and the vibrant spirit that makes ICCAD so special.

Warm regards,

Robert Wille General Chair Technical University of Munich, Munich Quantum Software Company, and Software Competence Center Hagenberg GmbH

Deming Chen Program Chair University of Illinois Urbana-Champaign

Ismail S. K. Bustany Vice Program Chair AMD Tsung-Yi Ho.png Tutorial & Special Session Chair The Chinese University of Hong Kong

Ron Duncan Workshop Chair Synopsys

### **Awards**

### William J. McCalla ICCAD Best Paper Award -

Frontend: TBA

Backend: TBA

**ICCAD 10 Year Retrospective Most Influential Paper Award**

TBA

2025 Outstanding Service Recognition Award

Jinjun Xiong (University at Buffalo)

"for outstanding service to the EDA Community as ICCAD General

Chair in 2024"

# Awards (cont.)

#### **Best Reviewer Award**

BaekGyu Kim, Daegu Gyeongbuk Institute of Science and Technology, South Korea Chen Zhang, Shanghai Jiao Tong University, China Fan Chen, Indiana University Bloomington, USA Tathagata Srimani, CMU, USA Yukai Chen, IMEC, Belgium

This award recognizes the dedicated service of reviewers and the outstanding quality of reviews received by TPC members. The awardees above were selected from a pool of candidates nominated by the TPC Track co-chairs, based on the following criteria:

- Insightfulness and Clarity: detailed comments with strong insights, e.g., feedback is clear and specific without vagueness.

- Thoroughness and Quality: thorough and high quality, e.g., comments are comprehensive and address both strengths and areas for improvement.

- Originality of Contribution: own review instead of relying on the secondary reviewer.

- Consistency and Fairness: the review scores should be consistent with the review content; overall tone and recommendations align with the content of the feedback.

- Impact on Authors: consider whether the review would genuinely help the author improve their work (a key sign of a high-quality review).

- Professionalism: ensure the review is respectful, free of bias, and professionally written.

### **BPA Candidates (Front End)**

**26:** GauPRE: A Pattern-based Rendering Engine for Gaussian Splatting on Edge Device Yuzheng Lin {1}, Lizhou Wu {1}, Chixiao Chen {2}, Xiaoyang Zeng {3}, Haozhe Zhu {3} {1} State Key Laboratory of Integrated Chips & Systems, Frontier Institute of Chip and System, Fudan University, China; {2} Fudan University, China; {3} State Key Laboratory of Integrated Chips & Systems, Fudan University, China

### 44: Perturbation-efficient Zeroth-order Optimization for Hardware-friendly On-device Training

Qitao Tan  $\{1\}$ , Sung-En Chang  $\{2\}$ , Rui Xia  $\{3\}$ , Huidong Ji  $\{4\}$ , Chence Yang  $\{1\}$ , Ci Zhang  $\{1\}$ , Jun Liu  $\{2\}$ , zheng zhan  $\{2\}$ , Zhenman Fang  $\{5\}$ , zhuo zou  $\{4\}$ , Yanzhi Wang  $\{2\}$ , Jin Lu  $\{1\}$ , Geng Yuan  $\{1\}$

{1} University of Georgia, United States; {2} Northeastern University, United States; {3} University of Pennsylvania, United States; {4} Fudan University, China; {5} Simon Fraser University, Canada

# **79: ExactMap: Enhancing Delay Optimization in Parallel ASIC Technology Mapping** Zhenxuan Xie {1}, Lixin Liu {2}, Tianji Liu {1}, Evangeline Young {1}

{1} The Chinese University of Hong Kong, Hong Kong Special Administrative Region of China; {2} The Chinese University of Hong Kong, Chin

# **265:** CLASS: A Controller-Centric Layout Synthesizer for Dynamic Quantum Circuits Yu Chen $\{1\}$ , Yilun Zhao $\{2\}$ , Bing Li $\{3\}$ , He Li $\{4\}$ , Mengdi Wang $\{1\}$ , yinhe han $\{5\}$ , Ying Wang $\{6\}$

{1} Institute of Computing Technology, Chinese Academy of Sciences, China; {2} Institute of Computing Technology, CAS, China; {3} Capital Normal University, China; {4} Southeast University., China; {5} Institute of Computing Technology, Chinese Academy of Sciences, China; {6} State Key Laboratory of Computer Architecture, Institute of Computing Technology, Chinese Academy of Sciences, China

### 537: Pathfinder: Constructing Cycle-accurate Taint Graphs for Analyzing Information Flow Traces

Katharina Ceesay-Seitz {1}, Flavien Solt {2}, Alexander Klukas {1}, Kaveh Razavi {1} {1} ETH Zurich, Switzerland; {2} UC Berkeley, United States

### 561: FAB: Fast and Demand-Aware Bandwidth Allocation Method for Wavelength-Routed Optical Networks-on-Chip

Liaoyuan Cheng, Mengchu Li, Zhidan Zheng, Tsun-Ming Tseng, Ulf Schlichtmann Technical University of Munich, Germany

### 1148: MIRAGE: Microarchitectural Footprints for Detecting Adversarial Attacks in One-Shot Inference

Soumi Chatterjee {1}, Debadrita Talapatra {1}, Nimish Mishra {1}, Aritra Hazra {2}, Debdeep Mukhopadhyay {3}

- {1} Indian Institute of Technology Kharagpur, India; {2} Dept of CSE, IIT Kharagpur, India;

- {3} Department of Computer Science and Engineering, Indian Institute of Technology Kharagpur, India

# **BPA Candidates (cont.)**

### 1239:LaZagna: An Open-Source Framework for Flexible 3D FPGA Architectural Exploration

Ismael Youssef {1}, Hang Yang {1}, Cong "Callie" Hao {2} {1} Georgia Tech, United States; {2} Georgia Institute of Technology, United States

**1318:** e-boost: Boosted E-Graph Extraction with Adaptive Heuristics and Exact Solving Jiaqi Yin {1}, Zhan Song {1}, Chen Chen {1}, Yaohui Cai {2}, Zhiru Zhang {2}, Cunxi Yu {1} {1} University of Maryland, College Park, United States; {2} Cornell University, United States

# **BPA Candidates (Back End)**

### 85: COBRA: Algorithm-Architecture Co-optimized Binary Transformer Accelerator for Edge Inference

Ye Qiao, Zhiheng Chen, Yian Wang, Yifan Zhang, Yunzhe Deng, Sitao Huang University of California, Irvine, United States

### 95: GTA: GPU-Accelerated Track Assignment with Lightweight Lookup Table for Conflict Detection

Chunyuan Zhao, Jiarui Wang, Xun Jiang, Jincheng Lou, Yibo Lin Peking University, China

### 554: LMLitho: A Large Vision Model-Driven Lithography Simulation Framework

Zhen Wang  $\{1\}$ , Hongquan He  $\{1\}$ , Tao Wu  $\{1\}$ , Xuming He  $\{2\}$ , Qi Sun  $\{3\}$ , Cheng Zhuo  $\{3\}$ , Bei Yu  $\{4\}$ , Jingyi Yu  $\{1\}$ , Hao Geng  $\{1\}$

{1} ShanghaiTech University, China; {2} ShanghaiTech University, China; {3} Zhejiang University, China; {4} The Chinese University of Hong Kong, Hong Kong Special Administrative Region of China

### 582: Semidefinite Programming-Based Decoupling Capacitor Placement for Power Distribution Network Optimization

Zong-Ying Cai  $\{1\}$ , Wei-Han Mao  $\{1\}$ , Yao-Wen Chang  $\{1\}$ , Yang Lu  $\{2\}$ , Jerry Bai  $\{2\}$ , Bin-Chyi Tseng  $\{2\}$

{1} National Taiwan University, Taiwan; {2} ASUSTeK Computer Inc., Taiwan

### 821: TickTockStack: In-Datapath Current Imbalance Elimination Using Clocked Differential Logic in a Voltage Stacked Vector Processor

Michal Gorywoda, Wanyeong Jung KAIST, Republic of Korea

#### 860: Leveraging GPU for Better Detailed Placement Quality

Chen-Han Lu {1}, Wen-Hao Liu {2}, Haoxing Ren {3}, Ting-Chi Wang {1} {1} National Tsing Hua University, Taiwan; {2} Nvidia, Taiwan; {3} NVIDIA Corporation, United States

### 926: Diff-DiT: Temporal Differential Accelerator for Low-bit Diffusion Transformers on FPGA

Shidi Tang {1}, Pengwei Zheng {2}, Ruiqi Chen {3}, Yuxuan Lv {2}, Bruno Silva {3}, Ming Ling {2}

{1} southeast university, China; {2} Southeast University, China; {3} Vrije Universiteit Brussel, Belgium

# 1008: The Fellowship of the Leak: Power Analysis of a Masked FrodoKEM Hardware Accelerator

Martin Schmid {1}, Giuseppe Manzoni {1}, Aydin Aysu {2}, Elif Bilge Kavun {3} {1} University of Passau, Germany; {2} North Carolina State University, United States; {3} Barkhausen Institut & TU Dresden, Germany

### **BPA Candidates (cont.)**

### 1231: dyGRASS: Dynamic Spectral Graph Sparsification via Localized Random Walks on GPUs

Yihang Yuan {1}, Ali Aghdaei {2}, Zhuo Feng {1}

{1} Stevens Institute of Technology, United States; {2} University of California San Diego, United States

### 1298: 3D Acceleration for Mixture-of-Experts and Multi-Head Attention Spiking Transformers with Dynamic Head Pruning

Boxun Xu {1}, Junyoung Hwang {2}, Pruek Vanna-iampikul {3}, Yuxuan Yin {1}, Sung Kyu Lim {4}, Peng Li {1}

{1} University of California, Santa Barbara, United States; {2} Georgia Institute of Technology, United States; {3} Burapha University, Thailand; {4} Georgia Tech, United States

# Enabling the Design of the Al World

Scan the QR to learn more!

# **Plenary Speakers**

The Quest for Energy Efficient Generative AI

Monday | October 27, 2025 | 8:30 - 9:30

Room: Ballroom A+B

Diana Marculescu, University of Texas at Austin

**Abstract:** Artificial Intelligence (AI) applications have entered and impacted our lives unlike any other technology advance from the recent past. While current

Al tools are approaching Artificial General Intelligence (AGI) capabilities, large gaps persist due to diminished benefits despite deploying enormous computing and ever-increasing energy demands. This quandary requires a holistic approach in determining energy efficient solutions for achieving AGI. While the holy grail for judging the quality of an AI model has largely been serving accuracy, and only recently its resource usage, neither of these metrics translate directly to energy efficiency, latency, or mobile device battery lifetime. More recently, generative AI relying on transformer, diffusion, or state-space models have revolutionized the way we approach reasoning and learning tasks across all types of modalities, from image to video and language, bringing increased performance at the expense of significant hardware costs.

Driven by AI – Driving Requires More Compute Than Ever

Tuesday | October 28, 2025 | 8:00 - 9:00

Room: Ballroom A+B

Hans-Jörg Vögel, BMW Group

**Abstract:** Higher levels of automation in road transport mobility are a true moonshot. Very few OEMs have so far

successfully obtained road approval for their Level 3 automated driving system, BMW being one of them. All already now is a major technological driving force behind automated driving and will continue to be. We will highlight current frontiers of All development in safety relevant systems and explore, how expected evolution of the technology will influence the road ahead for automated driving functions. Growth in sensor data volume and machine learning compute demand is fuelling a race to ever more potent embedded systems. Just brute-forcing hardware will not do. Innovative semiconductor solutions such as chiplets come to the rescue. As does intelligent hardware-software-co-design.

# Plenary Speakers (cont.)

End-to-end Open Source Platforms in the era of Domain-Specific Design Automation

Wednesday | October 29, 2025 | 8:00 - 9:00 Room: Ballroom A+B

Luca Benini, Universita di Bologna

**Abstract:** Modern computing workloads, from generative AI, to digital twins, to fully homomorphic

encryption, require sustained energy efficiency improvements, which cannot be matched simply by technology evolution. To tackle the challenge, we need to aggressively optimize computing platforms leveraging specialization across all levels of the design hierarchy, pushing into domain-specific design automation tools and methodologies. In this talk, I will give concrete examples of deep domain specialization, emphasizing the strategic importance of an end-to-end (models,software, instruction set architecture, digital IPs, EDA tools) open-platform approach to achieve the ultimate efficiency, while promoting a healthy innovation ecosystem.

### **Tutorial Sessions**

### Silence of the Chips: Advanced Techniques in Hardware Vulnerability Detection

### Monday | October 27, 2025 | 10:00 - 11:30

The ever-increasing complexity of microprocessors has resulted in several potent security threats in recent years. These vulnerabilities in the hardware arising from unchecked performance optimizations have been exploited through various ways, such as microarchitectural attacks, fault injections, memory corruption, and other forms of information leakage. Post tape-out, hardware vulnerabilities are typically mitigated using software updates or hardware recall, which result in unacceptably high performance or economic overheads, respectively. Thus, there is a pressing need to uncover these vulnerabilities during the hardware design phase. Integrating such approaches can improve the overall security, reliability, and economic viability of microprocessors. In this tutorial, we introduce hardware vulnerabilities and state-of-the-art techniques to uncover these vulnerabilities at design time, leveraging hardware fuzzing, AI, and formal verification. Tutorial participants will gain an understanding of the fundamentals of hardware vulnerabilities, their origins, and detection approaches. We will present some of the potent Common Weakness Enumerations (CWEs) we have exposed in popular microprocessors. With our assistance, participants will get a real-world demonstration of the hardware fuzzing techniques used to detect these vulnerabilities and pinpoint their location in hardware design. We will explore the recent advances in hardware fuzzing using AI techniques and formal verification. We will use concrete, hands-on examples to quantitatively analyze the potential of these techniques for hardware security and the open challenges in the domain.

Ahmad-Reza Sadeghi TU Darmstadt

JV Rajendran Texas A&M University

Nikhilesh Singh TU Darmstadt

Lichao Wu TU Darmstadt

Huimin Li TU Darmstadt

Chen Chen Texas A&M University

Mohamadreza Rostami TU Darmstadt

### **Tutorial Sessions (cont.)**

Quantum Machine Learning Foundations for Quantum Architecture Design and Future Quantum EDA

### Monday | October 27, 2025 | 13:00 - 14:30

This tutorial explores the intersection of quantum machine learning (QML) and the design of quantum architectures, highlighting foundational techniques that pave the way for future quantum-enabled design automation (Quantum EDA). Rather than optimizing classical semiconductor flows, we focus on how QML, quantum reinforcement learning (QRL), and quantum architecture search (QAS) can be applied to discover, optimize, and innovate quantum circuits and variational architectures. Through interactive, hands-on sessions using open-source quantum simulators such as Qiskit and PennyLane, participants will engage with key methodologies for quantum model design and architectural optimization. This session is aimed at future explorers — those who seek to rethink design automation in the quantum era — and no prior knowledge of traditional EDA is required.

Samuel Yen-Chi Chen Wells Fargo

Zhiding Liang Rensselaer Polytechnic Institute

Kuan-Chen Chen Imperial College London

# Workshops

### Top Picks in Hardware and Embedded Security

### Thursday | October 30, 2025 | 8:00 - 16:30

Top Picks Workshop creates a venue to showcase the best and high impact recently published works in the area of hardware and embedded security. These works will be selected from conference papers that have appeared in leading hardware security conferences including but not limited to DAC, ICCAD, DATE, ASPDAC, HOST, Asian HOST, GLSVLSI, VLSI Design, CHES, ETS, VTS, ITC, S&P, Usenix Security, CCS, NDSS, ISCA, MICRO, ASPLOS, HPCA, HASP, ACSAC, Euro S&P, and Asia CCS. The 8th Top Picks workshop will be collocated with ICCAD 2025. The authors of a short list of papers picked from the submissions are required to present their work at the workshop on October 30, 2025 and are invited to attend ICCAD's networking in—person on October 30, 2025. The presentation including a discussion (Q&A) session, is mandatory.

Ahmad-Reza Sadeghi Technical University of Darmstadt Darmstadt, Hesse, Germany

Xiaolin Xu Northeastern University, USA

### SUSHI'25: Sustainable Hardware Security

### Thursday | October 30, 2025 | 8:00 - 16:30

The pursuit of digital sovereignty, global semiconductor shortages, and geopolitical interests drive worldwide initiatives to bolster semiconductor technology and manufacturing. Hardware security is vital at the core of all computing systems, as insecure hardware puts critical systems and society at risk. However, in recent years we are observing the discovery of a growing number of hardware design and implementation vulnerabilities that unprivileged software could exploit, leading to the potential exposure of sensitive data or compromise of the whole computing system. This new attack paradigm greatly shadows decades of system security research. Existing solutions are often ad-hoc, limited, inefficient, specific. Tackling these challenges calls for radically new approaches to the security-by-design for hardware, security-aware electronic design automation, resilient microarchitecture and architectures, and scalable assurance.

Jason Fung Intel

Cliff Wang NSF

Workshop on Post-Quantum Cryptography Resilience, Verification, and Secure Design Automation (WPQC)

### Thursday | October 30, 2025 | 8:00 - 16:30

The rapid transition toward Post-Quantum Cryptography (PQC) has prompted a global effort to redefine digital security in anticipation of quantum-capable adversaries. While PQC algorithms are mathematically robust, their secure and efficient integration into hardware systems introduces new vulnerabilities and engineering challenges - especially in areas such as side-channel resistance, hardware/software co-design, and formal verification. The Workshop on Post-Quantum Cryptography and Secure Hardware (WPQC) aims to address these challenges by serving as a dedicated forum for researchers and practitioners in hardware security, EDA/CAD, computer architecture, and cryptography. The workshop provides a platform to explore the intersection of PQC and hardware/system design, highlighting recent advancements in secure accelerator development, design automation, system integration, and emerging threat models. By bringing together experts from academia, industry, and standardization bodies, WPQC seeks to accelerate collaborative research efforts and foster a shared vision for building resilient, verifiable, and efficient post-quantum systems.

Shivam Bhasin NTU (Singapore)

Trevor E. Carlson NUS (Singapore)

Mona Hashemi NUS (Singapore)

Reza Azarderakhsh FL Atlantic U, and PQSecure (USA)

Mojtaba Bishehniasar Microsoft (USA)

### 2nd Quantum Computing Applications and Systems (QCAS)

### Thursday | October 30, 2025 | 8:00 - 16:30

Our proposed workshop aims to address emerging challenges and explore innovative solutions in the field of quantum technologies, particularly focusing on quantum computing applications for real-world problems. Quantum technologies are becoming crucial in a variety of scientific domains including chemistry, finance, power systems, etc. Our workshop will bring together researchers, practitioners, and industry experts to exchange ideas, share applications, and discuss the latest advancements in quantum algorithms, error correction, control techniques, and their applications across diverse fields. This event will serve as a platform to showcase cutting-edge research, foster collaboration, and drive innovation in the intersection of CAD, optimization, machine learning, and quantum computing.

Robert Wille TUM, MQSC, SCCH

Martin Schulz Technical University of Munich, Germany

Samuel Yen-Chi Chen Wells Fargo

Yosuke Ueno Riken

### System-Level Interconnect Pathfinding (SLIP)

### Thursday | October 30, 2025 | 8:00 - 16:30

SLIP, co-located with ICCAD, brings together researchers and practitioners who have a shared interest in the challenges and futures of system-level interconnect, coming from wide-ranging backgrounds that span system, application, design and technology.

The technical goal of the workshop is to

- identify fundamental problems, and,

- foster new pathfinding of design, analysis, and optimization of system-level interconnects with emphasis on system-level interconnect modeling and pathfinding, DTCO-enhanced interconnect fabrics, memory and processor communication links, novel dataflow mapping for machine learning, 2.5/3D architectures, and new fabrics for the beyond-Moore era.

Original submissions in the form of regular technical papers, invited sessions (tutorials, panels, special-topic sessions), workshop discussion topics, and posters are welcome. Program content is accepted based on novelty and contributions to the advancement of the field. Authors will keep the copyright of their work and there will be no published proceedings.

#### Foundation Models and EDA

### Thursday | October 30, 2025 | 8:00 - 11:30

The rapid advancement of foundation models has brought powerful new capabilities to Electronic Design Automation (EDA). Unlike traditional task-specific Artificial Intelligence (AI) approaches, foundation models leverage self-supervised learning and large-scale data pre-training to acquire strong generalization abilities. These models can then be efficiently fine-tuned on EDA-specific datasets, enabling a wide range of downstream applications such as hardware code generation, debug and optimization, EDA agents, circuit representation learning and understanding, etc.

This workshop aims to foster collaboration among researchers, engineers, and industry experts to explore the evolving intersection of foundation models and EDA methodologies. By identifying key challenges and exchanging ideas, we seek to inspire comparative analysis between the unique demands of EDA and those of other application domains, and to promote novel solutions that leverage the strengths of foundation models for more accurate, efficient, and scalable design automation. Through talks, paper presentations, and interactive discussions, the workshop will showcase recent progress and explore new ways to apply foundation models in EDA—helping to drive innovation and advance the future of intelligent circuit design.

Deming Chen University of Illinois

Igor Markov Synopsys

Guohao Dai Shanghai Jiao Tong University

Siddharth Garg NY University

Grace Li Zhang TU Darmstadt

Zhengyuan Shi Chinese University of Hong Kong

Automotive Chiplet Platform: Solutions Enabled by Industry and Academic Collaboration

### Thursday | October 30, 2025 | 13:00 - 16:30

Chiplet-based platform is a pragmatic solution to meet the automotive industry's growing demands for performance, longevity, and cost-efficiency. Such platforms enable modular, scalable integration of diverse processing units (like CPUs, GPUs, and AI accelerators) across different process nodes, improving design flexibility, yield, and reliability, which is critical in safety-driven environments. They also support thermal and power optimization, simplify long-term maintenance and supply chain challenges, and align well with emerging zonal E/E architectures. The purpose of the workshop is to outline the challenges and novel solutions to enable chiplet-based computing platform for automotive domain.

### **Panel Session**

### Revolution or Hype? Seeking the Limits of Large Models in Hardware Design

### Tuesday | October 28, 2025 | 9:30 - 11:00

Recent breakthroughs in Large Language Models (LLMs) and Large Circuit Models (LCMs) have sparked excitement across the electronic design automation (EDA) community, promising significant advances in circuit design and optimization. Yet, skepticism persists: Are these large AI models truly transformative, or are we experiencing a temporary wave of inflated expectations? This panel brings together leading experts from academia and industry to critically examine the practical capabilities, limitations, and future prospects of large AI models in hardware design. Panelists will debate their reliability, scalability, interpretability, and whether these models meaningfully outperform and/or complement traditional EDA methods—offering attendees fresh insights into one of today's most contentious and impactful technology trends.

Moderator Grace Li Zhang TU Darmstadt

Xi Wang Southeast University

Qiang Xu National Technology Innovation Center for EDA, China

Rolf Drechsler University of Bremen

Leon Stok IBM

Igor L. Markov Synopsys

### **CEDA Luncheon**

From Past to Future: 20 Years of EDA Wisdom and What's Next

Monday | October 27, 2025 | 11:30 - 13:00

Over the past two decades, the EDA community and industry have made significant contributions to enabling productive chip designs and driving the overall progress and growth of semiconductor technology. Looking ahead, EDA faces ongoing challenges and opportunities in a rapidly evolving landscape, largely fueled by the phenomenal advances in ML/AI technologies. How can we seize these opportunities while addressing the evergrowing complexity of chip design and the relentless demands of the market? In this panel, four distinguished experts from academia and industry around the world will share insights on lessons learned from the past and their visions for the future.

#### **Panelists**

Norbert Wehn RPTU, Germany

Shaojun Wei Tsinghua University, China

Sani Nassif Radyalis, USA

Subhasish Mitra Stanford University, USA

#### **Moderators**

L. Miguel Silveira IEEE CEDA President

Robert Wille TUM, MQSC, SCCH

# **Workforce Development**

#### **Student Research Competition**

Posters: Monday | October 27, 2025 | 19:00 - 20:30

Oral Presentations: Tuesday | October 28, 2025 | 12:30 - 14:00

The ACM Student Research Competition (SRC) provides undergraduate and graduate students who are ACM members with a unique opportunity to present their work, exchange ideas, and gain recognition from the international computing community. Organized by ACM SIGDA and hosted at ICCAD 2025, the competition features poster and presentation sessions where students showcase their research in design automation. Participants benefit from feedback by experts, networking with academic and industry leaders, and the chance to win prizes. Separate categories for undergraduate and graduate students ensure fair evaluation, with submissions judged on novelty, technical merit, and contributions to the field.

#### Job Fair

#### Tuesday | October 28, 2025 | 18:00 - 19:00

ACM SIGDA and IEEE CEDA will host the 4th annual EDA Job Fair at ICCAD 2025, providing students and professionals the opportunity to connect with leading companies and academic institutions. Attendees can learn about current openings, network directly with recruiters, and explore career opportunities in electronic design automation. Participants are encouraged to submit their CVs in advance, and ICCAD registration (minimum one-day) is required.

#### CADathlon@ICCAD 2025

#### Sunday | October 26, 2025 | 8:00 - 17:00

The CADathlon is a challenging, all-day programming competition focusing on practical problems at the forefront of Computer-Aided Design and Electronic Design Automation in particular. The contest emphasizes the knowledge of algorithmic techniques for CADapplications, problem-solving and programming skills, and teamwork.

As the "Olympic games of EDA," the contest brings together the best and the brightest of the next generation of CAD professionals. It gives academia and the industry a unique perspective on challenging problems and rising stars, and it also helps attract top graduate students to the FDA field.

### **Social Functions**

#### Welcome Reception

### Monday | October 27, 2025 | 19:00 - 20:30 | The Westin Grand Munich

All conference registrants are invited to join us for the Welcome Reception on Monday, October 27, at The Westin Grand Munich. Start the conference on a high note with an evening of networking, hors d'oeuvres, and refreshments as you connect with fellow attendees in a relaxed and friendly setting. We look forward to welcoming you in Munich!

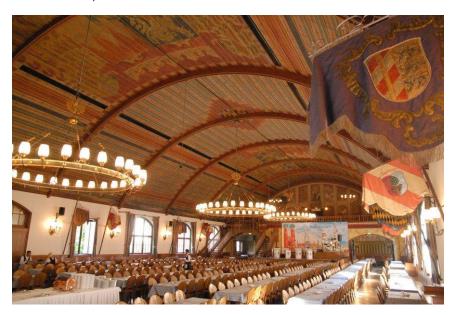

#### **ACM SIGDA Gala Dinner**

### Wednesday | October 29, 2025 | 18:30 - 20:00 | Hofbräuhaus München Festsaal

Join us for an unforgettable evening at the historic Hofbräuhaus München Festsaal, featuring a nine-meter-high barrel vault and classic Bavarian ambiance. Enjoy traditional food, drinks, and lively conversation in one of Munich's most iconic venues. Access is included with your conference registration—no additional ticket required. Attendees are responsible for their own transportation to and from the venue.

Address: Platzl 9, 80331 München

# **Sponsors & Exhibitors**

**Platinum Sponsor**

SYNOPSYS"

ACADEMIC & RESEARCH ALLIANCES

**Gold Sponsors**

cādence

Silver Sponsors

Sony Al

Open Innovation Platform®

# **Sponsors & Exhibitors**

### **Conference Sponsors**

|               | Sunday, October 26, 2025                |

|---------------|-----------------------------------------|

| 7:30 - 8:00   | Room: Foyer Ballroom                    |

| 8:00 - 6:00   | CADathion Breakfast<br>Room: Atlanta    |

| 9:00 - 12:00  | CADathlon Room: Atlanta                 |

| 12:00 - 13:00 | CADathlon Lunch<br>Room: Atlanta        |

| 13:00 - 15:00 | CADathlon Room: Atlanta                 |

| 15:00 - 15:30 | CADathion Coffee Break<br>Room: Atlanta |

| 15:30 - 17:00 | CADathlon<br>Room: Atlanta              |

| Time          | Sydney                                                                                                            | Barcelona                                                                             | Monday, October 27, 2025 Atlanta                                                                        | 2025<br>Athen                                                                                                         | Rome                                                                                        | Montreal                                                                                                                  |

|---------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| 7:00 - 8:00   | (ample                                                                                                            |                                                                                       | Registration   Room: Foyer Ballroom                                                                     | n: Foyer Ballroom                                                                                                     |                                                                                             |                                                                                                                           |

| 8:00 - 8:30   |                                                                                                                   |                                                                                       | Opening Ceremony   Room: Ballroom A+B                                                                   | oom: Ballroom A+B                                                                                                     |                                                                                             |                                                                                                                           |

| 8:30 - 9:30   |                                                                                                                   |                                                                                       | Keynote: Diana Marculescu   Room: Ballroom A+B                                                          | I   Room: Ballroom A+B                                                                                                |                                                                                             |                                                                                                                           |

| 9:30 -10:00   |                                                                                                                   |                                                                                       | Coffee Break   Exhibits   Room: Foyer Ballroom                                                          | Room: Foyer Ballroom                                                                                                  |                                                                                             |                                                                                                                           |

| 10:00 - 11:30 | Tutorial:<br>Silence of the Chips: Advanced<br>Techniques in Hardware<br>Vulnerability Detection                  | Technical Session: Speeding<br>and Learning for Achieving 2D<br>and 3D Design Closure | Special Session:<br>Agile and Open Hardware<br>Design and Verification                                  | Technical Session: Hardware<br>Assurance in the Adversarial<br>Era: Camouflage, Detection,<br>and Lightweight Defense | Technical Session: Memory<br>and Storage Design<br>Optimization Techniques                  | Technical Session: Journey<br>from Efficient Layoutto<br>Successful Wafer                                                 |

| 11:30 - 13:00 |                                                                                                                   |                                                                                       | CEDA Luncheon Panel   Room: Ballroom A+B                                                                | Room: Ballroom A+B                                                                                                    |                                                                                             |                                                                                                                           |

| 3:00 - 14:30  | Tutorial:<br>Quantum Machine Learning<br>Foundations for Quantum<br>Architecture Design and<br>Future Quantum EDA | Technical Session:<br>Processing-in-Memory (PIM/<br>CIM) Powered Al Acceleration      | Special Session: Hardware-Software Co- Design for highly Optimized, Customized, and Reliable Al Systems | Technical Session: Logic<br>Synthesis Reimagined:<br>Mapping, Rewriting, and<br>Structural Optimization               | Technical Session: Hardware<br>Reliability and Testing                                      | Technical Session:<br>Silicon Whispers: Side<br>Channels, Rowhammer, and<br>Microarchitectural Leaks                      |

| 14:30 - 15:00 |                                                                                                                   |                                                                                       | Coffee Break   Exhibits   Room: Foyer Ballroom                                                          | Room: Foyer Ballroom                                                                                                  |                                                                                             |                                                                                                                           |

| 15:00 - 16:30 | Special Session:<br>EDA from GPU Acceleration to<br>GPU Exploration                                               | Technical Session: Edge<br>Intelligence: Co-Design,<br>Resilience, and Efficiency     | Special Session:<br>Security Challenges and<br>Opportunities in In-Sensor<br>Computing Systems          | Technical Session: Power<br>and Performance Conscious<br>Hardware Design                                              | Technical Session: Advanced<br>Modeling and Optimization for<br>Power and Thermal Integrity | Technical Session: In memory<br>computing and computing in<br>memory                                                      |

| 16:30 - 16:45 |                                                                                                                   |                                                                                       | Transition                                                                                              | ition                                                                                                                 |                                                                                             |                                                                                                                           |

| 16:45 - 17:45 | Technical Session: Edge-<br>Intelligent: Co-Design and<br>Compression for Efficient Al<br>at the Edge             | Technical Session: Advancing<br>towards the Optimum Cell<br>Generation                | Technical Session: Learning-<br>Based Hardware Optimization<br>and Scheduling                           | Technical Session: Timing<br>Optimization and Optical<br>Routing                                                      | Technical Session:<br>Optimization and Simulation<br>From Circuits to Systems               | Technical Session: Emerging<br>Architectures and Automation<br>for Neuromorphic, In-Memory,<br>and Microfluidic Computing |

| 18:00 - 19:00 |                                                                                                                   |                                                                                       | Synopsys Sponsor Session   Room: Ballroom A+B'                                                          | Room: Ballroom A+B"                                                                                                   |                                                                                             |                                                                                                                           |

Welcome Reception & SRC Poster Session | Room: Foyer Ballroom"

19:00 - 20:30

|                           | Montreal  |                                     |                                               |                                                | Technical Session: Breaking the Thermal Wall: Emerging Thermal Simulation and Design for 2.5D/3D Systems |                            | Technical Session:<br>Brains and Bits: FPGA<br>Acceleration from Al to<br>SAT Solvers                                        |                                                | Technical Session:<br>Efficient Verification and<br>Debugging                                              |               | Technical Session:<br>Efficient Verification and<br>Debugging                                              |

|---------------------------|-----------|-------------------------------------|-----------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------|---------------|------------------------------------------------------------------------------------------------------------|

|                           | Rome      |                                     |                                               |                                                | Technical Session:<br>Accelerating Large<br>Language Models (LLMs)                                       |                            | Technical Session:<br>Reasoning and Debugging<br>in Hardware Design with<br>LLMs                                             |                                                | Technical Session: Next-Gen Acceleration: Sparsity, Vectors, and Reconfigurable Intelligence               |               | Technical Session:<br>Next-Gen Acceleration:<br>Sparsity, Vectors,<br>and Reconfigurable<br>Intelligence   |

| 3, 2025                   | Athen     | Registration   Room: Foyer Ballroom | Keynote: Hans-Jörg Vögel   Room: Ballroom A+B | Coffee Break   Exhibits   Room: Foyer Ballroom | Technical Session:<br>Perfecting Routing by All<br>Means                                                 | Lunch   Room: Ballroom A+B | Technical Session:<br>Addressing noise and<br>optimization of quantum<br>and photonic systems                                | Room: Foyer Ballroom                           | Technical Session:<br>System-level and<br>Architecture Design<br>Optimisation                              | ition         | Technical Session:<br>System-level and<br>Architecture Design<br>Optimisation                              |

| Tuesday, October 28, 2025 | Atlanta   | Registration   Roo                  | Keynote: Hans-Jörg Vögel                      | Coffee Break   Exhibits                        | Special Session:<br>Circuit and Architecture<br>Design with Emerging<br>Computing Paradigms              | Lunch   Room:              | Special Session:<br>Generative AI for At-Scale<br>and Unconventional<br>Analog/RFIC Design and<br>Automation                 | Coffee Break   Exhibits   Room: Foyer Ballroom | Special Session: Reimagining Scientific Computing with Neuromorphic and Analog Systems                     | Transition    | Special Session:<br>Reimagining Scientific<br>Computing with<br>Neuromorphic and Analog<br>Systems         |

|                           | Barcelona |                                     |                                               |                                                | Technical Session: Al<br>Analog Circuits Design<br>with Learning and<br>Reasoning                        |                            | Technical Session: How to<br>Become a Better Physical<br>Designer: Novel Tweaks<br>on Mapping, Partitioning<br>and Placement |                                                | Technical Session: FPGA<br>and Reconfigurable<br>Accelerators for AI<br>Models                             |               | Technical Session: FPGA<br>and Reconfigurable<br>Accelerators for AI<br>Models                             |

|                           | Sydney    |                                     |                                               |                                                | Panel: Revolution or Hype? Seeking the Limits of Large Models in Hardware Design                         |                            | Student Research<br>Competition (Oral<br>Presentations)                                                                      |                                                | Special Session: Fueling the Future: Achieving Reliable and Generalizable Data Foundations for LLMs in EDA |               | Special Session: Fueling the Future: Achieving Reliable and Generalizable Data Foundations for LLMs in EDA |

|                           | Time      | 7:30 - 8:00                         | 8:00 - 9:00                                   | 9:00 - 9:30                                    | 9:30 - 11:00                                                                                             | 11:00 - 12:30              | 12:30 - 14:00                                                                                                                | 14:00 - 14:30                                  | 14:30 - 16:00                                                                                              | 16:00 - 16:15 | 16:15 - 17:15                                                                                              |

Job Fair | Room: Foyer Ballroom

18:00 - 19:00

|                             | Rome      |                                     |                                           |                                                | Technical Session: Advanced<br>Architectures and Emerging<br>Models                                                      |                            | Technical Session: From Prediction to Closure: Intelligent Techniques for Timing Estimation and Optimization |                                                | Technical Session: From Prediction to Closure: Intelligent Techniques for Timing Estimation and Optimization |               | Technical Session: Hardware<br>for Neural Rendering and<br>Geometric Models    |

|-----------------------------|-----------|-------------------------------------|-------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------------|

|                             | Athen     | _                                   | A+B                                       | llroom                                         | Technical Session: Flow<br>Forward: Frameworks<br>and Optimizations for<br>Reconfigurable Accelerators                   |                            | Technical Session: Advancement for Next- generation IC-Design and Computing Paradigm                         | W00                                            | Technical Session: Advancement for Next- generation IC-Design and Computing Paradigm                         |               | Technical Session: Efficient Al<br>on Edge and LLM Infrastructure              |

| Wednesday, October 29, 2025 | Atlanta   | Registration   Room: Foyer Ballroom | Keynote: Luca Benini   Room: Ballroom A+B | Coffee Break   Exhibits   Room: Foyer Ballroom | Special Session: System-Level Design for Chiplets: Architecture Exploration and Resource Management                      | Lunch   Room: Ballroom A+B | Technical Session: Scalable<br>Simulation and Verification<br>Frameworks                                     | Coffee Break   Exhibits   Room: Foyer Ballroom | Technical Session: Scalable<br>Simulation and Verification<br>Frameworks                                     | Transition    | Technical Session: Multi-<br>Physics Modelling and<br>Advanced Integration     |

| Wednes                      | Barcelona | E .                                 | Keyn                                      | Coffee                                         | Technical Session: Multimodal<br>and Generative Intelligence<br>for EDA                                                  |                            | Technical Session: Hardware<br>Support for Security:<br>Confidential Computing with<br>Accelerators          | Coffe                                          | Technical Session: Hardware<br>Support for Security:<br>Confidential Computing with<br>Accelerators          |               | Technical Session: Memory-<br>Centric Systems: Design and<br>Optimizations     |

|                             | Sydney    |                                     |                                           |                                                | Special Session:<br>Cross-Layer Design for Health-<br>Centric Al Systems: Models,<br>Platforms, and Emerging<br>Hardware |                            | Special Session:<br>2025 CAD Contests at ICCAD                                                               |                                                | Special Session:<br>2025 CAD Contests at ICCAD                                                               |               | Special Session:<br>Bridging the Gap: Design<br>Automation Meets Microfluidics |

|                             | Time      | 7:30 - 8:00                         | 8:00 - 9:00                               | 9:00 - 9:30                                    | 9:30 - 11:00                                                                                                             | 11:00 - 12:30              | 12:30 - 14:00                                                                                                | 14:00 - 14:30                                  | 14:30 - 16:00                                                                                                | 16:00 - 16:15 | 16:15 - 17:15                                                                  |

ACM SIGDA Dinner | Location: Hofbräuhaus München Festsaal

18:30 - 20:00

| Thursday, October 30, 2025 | Montreal  | Room: Upstairs Foyer | Foundation Models and<br>EDA                                                                                     | Coffee Break<br>Room: Upstairs Foyer | Foundation Models and<br>EDA                                                                                     | Standing Lunch<br>Room: Foyer Area of Sydney and Atlanta | Automotive Chiplet<br>Platform: Solutions<br>Enabled by Industry and<br>Academic Collaboration                   | Coffee Break<br>Room: Upstairs Foyer | Automotive Chiplet<br>Platform: Solutions<br>Enabled by Industry and<br>Academic Collaboration                   |

|----------------------------|-----------|----------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------|

|                            | Rome      |                      | System-Level<br>Interconnect Pathfinding<br>(SLIP)                                                               |                                      | System-Level<br>Interconnect Pathfinding<br>(SLIP)                                                               |                                                          | System-Level<br>Interconnect Pathfinding<br>(SLIP)                                                               |                                      | System-Level<br>Interconnect Pathfinding<br>(SLIP)                                                               |

|                            | Athen     |                      | 2nd Quantum Computing<br>Applications and<br>Systems (QCAS)<br>Workshop                                          |                                      | 2nd Quantum Computing<br>Applications and<br>Systems (QCAS)<br>Workshop                                          |                                                          | 2nd Quantum Computing<br>Applications and<br>Systems (QCAS)<br>Workshop                                          |                                      | 2nd Quantum Computing<br>Applications and Systems<br>(QCAS) Workshop                                             |

|                            | Atlanta   |                      | SUSHI'25: Sustainable<br>Hardware Security                                                                       |                                      | SUSHI'25: Sustainable<br>Hardware Security                                                                       |                                                          | SUSHI'25: Sustainable<br>Hardware Security                                                                       |                                      | SUSHI'25: Sustainable<br>Hardware Security                                                                       |

|                            | Barcelona |                      | Top Picks in Hardware<br>and Embedded Security                                                                   |                                      | Top Picks in Hardware<br>and Embedded Security                                                                   |                                                          | Top Picks in Hardware<br>and Embedded Security                                                                   |                                      | Top Picks in Hardware<br>and Embedded Security                                                                   |

|                            | Sydney    |                      | Workshop on Post-<br>Quantum Cryptography<br>Resilience, Verification,<br>and Secure Design<br>Automation (WPQC) |                                      | Workshop on Post-<br>Quantum Cryptography<br>Resilience, Verification,<br>and Secure Design<br>Automation (WPQC) |                                                          | Workshop on Post-<br>Quantum Cryptography<br>Resilience, Verification,<br>and Secure Design<br>Automation (WPQC) |                                      | Workshop on Post-<br>Quantum Cryptography<br>Resilience, Verification,<br>and Secure Design<br>Automation (WPQC) |

|                            | Time      | 7:30 - 8:00          | 8:00 - 9:30                                                                                                      | 9:30 - 10:00                         | 10:00 - 11:30                                                                                                    | 11:30 - 13:00                                            | 13:00 - 14:30                                                                                                    | 14:30 - 15:00                        | 15:00 - 16:30                                                                                                    |

7:30 – 8:00 **CADathlon ONLY Registration Room**: Foyer Ballroom

8:00 - 9:00

CADathlon Breakfast Room: Atlanta

9:00 – 12:00 CADathlon Room: Atlanta

12:00 – 13:00 Lunch

Room: Atlanta

13:00 – 15:00 CADathlon Room: Atlanta

15:00 – 15:30 Coffee Break Room: Atlanta

15:30 – 17:00 CADathlon Room: Atlanta

The CADathlon is a challenging, all-day programming competition focusing on practical problems at the forefront of Computer-Aided Design and Electronic Design Automation in particular. The contest emphasizes the knowledge of algorithmic techniques for CADapplications, problem-solving and programming skills, and teamwork.

As the "Olympic games of EDA," the contest brings together the best and the brightest of the next generation of CAD professionals. It gives academia and the industry a unique perspective on challenging problems and rising stars, and it also helps attract top graduate students to the EDA field.

7:00 – 8:00 **Registration**

Room: Foyer Ballroom

8:00 - 8:30

Opening Ceremony Room: Ballroom A+B

8:30 - 9:30

Keynote: The Quest for Energy Efficient Generative AI

Diana Marculescu, University of Texas at Austin

Room: Ballroom A+B

Session Chair(s): Robert Wille, TUM, MQSC, SCCH

9:30 - 10:00

Coffee Break and Exhibits Room: Foyer Ballroom

10:00 - 11:30

Tutorial: Silence of the Chips: Advanced Techniques in Hardware Vulnerability

**Detection Room**: Sydney

The ever-increasing complexity of microprocessors has resulted in several potent security threats in recent years. These vulnerabilities in the hardware arising from unchecked performance optimizations have been exploited through various ways, such as microarchitectural attacks, fault injections, memory corruption, and other forms of information leakage. Post tape-out, hardware vulnerabilities are typically mitigated using software updates or hardware recall, which result in unacceptably high performance or economic overheads, respectively. Thus, there is a pressing need to uncover these vulnerabilities during the hardware design phase. Integrating such approaches can improve the overall security, reliability, and economic viability of microprocessors. In this tutorial, we introduce hardware vulnerabilities and state-of-the-art techniques to uncover these vulnerabilities at design time, leveraging hardware fuzzing, AI, and formal verification. Tutorial participants will gain an understanding of the fundamentals of hardware vulnerabilities, their origins, and detection approaches. We will present some of the potent Common Weakness Enumerations (CWEs) we have exposed in popular microprocessors. With our assistance, participants will get a real-world demonstration of the hardware fuzzing techniques used to detect these vulnerabilities and pinpoint their location in hardware design. We will explore the recent advances in hardware fuzzing using AI techniques and formal verification. We will use concrete, hands-on examples to quantitatively analyze the potential of these techniques for hardware security and the open challenges in the domain.

10:00 - 11:30

Hardware Assurance in the Adversarial Era: Camouflage, Detection, and Lightweight Defense

Room: Athens

Session Chair(s): Debdeep Mukhopadhyay, Indian Institute of Technology Kharagpur Elif Bilge Kavun, Technische Universitat Dresden

This session explores emerging techniques for securing hardware against adversarial threats. Topics include ML-driven camouflaging, RL-based Trojan detection, X-ray fingerprinting for trust verification, and lightweight defenses against bit-flip and inference attacks. Also featured are efficient hardware accelerators for post-quantum cryptography. Together, these works advance the state of resilient and trustworthy hardware design.

10:00

### 395: Designing with Deception: ML- and Covert Gate-Enhanced Camouflaging to Thwart IC Reverse Engineering

Junling Fan, David Koblah, Domenic Forte University of Florida, United States

10:15

### 771: Defense in the Reverse Fragment: RL-Based Partial Netlist Hardware Trojan Detection

Bolun Li, Chen Dong, Decheng Qiu, Mingzhi Chen, Yang Yang Fuzhou University, China

10:30

#### 1043: TREX-F: TRustability of Electronics using X-ray based Fingerprinting

Tishya Sarma Sarkar {1}, Shuvodip Maitra {2}, Abhishek Chakraborty {2}, Sarani Bhattacharya {2}, Debdeep Mukhopadhyay {3}

{1} IIT, Kharagpur, India; {2} Indian Institute of Technology Kharagpur, India; {3} Department of Computer Science and Engineering, Indian Institute of Technology Kharagpur, India

10:45

#### 1148: MIRAGE: Microarchitectural Footprints for Detecting Adversarial Attacks in One-Shot Inference

Soumi Chatterjee  $\{1\}$ , Debadrita Talapatra  $\{1\}$ , Nimish Mishra  $\{1\}$ , Aritra Hazra  $\{2\}$ , Debdeep Mukhopadhyay  $\{3\}$

- {1} Indian Institute of Technology Kharagpur, India; {2} Dept of CSE, IIT Kharagpur, India;

- {3} Department of Computer Science and Engineering, Indian Institute of Technology Kharagpur, India

11:00

### 772: LEAF: Lightweight and Efficient Hardware Accelerator for Signature Verification of FALCON

Samuel Coulon {1}, Jinjun Xiong {2}, Jiafeng Xie {1}

{1} Villanova University, United States; {2} University at Buffalo, United States

11:15

# 1245: Non-Negative AdderNet: Algorithm-Hardware Co-design for Lightweight Defense of Bit-Flip Attacks

Yunxiang Zhang {1}, Sabbir Ahmed {2}, Abeer Almalky {2}, Adnan Siraj Rakin {3}, Wenfeng Zhao {3}

{1} Binghamton university, United States; {2} Binghamton University (SUNY), United States; {3} Binghamton University, United States

10:00 - 11:30

#### Journey from Efficient Layout to Successful Wafer

Room: Montreal

Session Chair(s): Ing-Chao Lin, National Yang Ming Chiao Tung University

Yuzhe Ma, The Hong Kong University of Science and Technology

(Guangzhou)

As the complexity of VLSI design has soared, it has become very challenging to ensure that the designs can actually be manufactured with high yield and reliability. This session will provide valuable insights into the intricate steps that contribute to the successful transition from VLSI layout to a wafer. We will delve into the critical aspects of layout efficiency, exploring various techniques and methodologies that ensure optimal performance and reliability. Additionally, we will discuss lithography simulation framework and advanced techniques for yield analysis and optimization.

10:00

### **832:** GeoFA: A Geometric Finite Automaton Engine for Efficient Layout Pattern Matching qingsheng qiu {1}, ziwen zheng {2}, boyu shi {1}, chao wang {1}

{1} southeast university, China; {2} southeast university

10:15

#### 1179: G-Contour: GPU Accelerated Contour Tracing For Large-Scale Layouts

Shuo Yin  $\{1\}$ , Jiahao Xu  $\{1\}$ , Jiaxi Jiang  $\{1\}$ , Mingjun Li  $\{1\}$ , Yuzhe Ma  $\{2\}$ , Tsung-Yi Ho  $\{1\}$ , Bei Yu  $\{1\}$

{1} The Chinese University of Hong Kong, Hong Kong Special Administrative Region of China; {2} The Hong Kong University of Science and Technology (Guangzhou), China

10:30

# 432: 3D DRC: Design Rule Checking for 3D IC with U-Net-based Non-Manhattan Optimization

Shunjie Chang, Youran Wu, Jianli Chen, Jun Yu, Kun Wang Fudan University, China

10:45

#### 554: LMLitho: A Large Vision Model-Driven Lithography Simulation Framework

Zhen Wang  $\{1\}$ , Hongquan He  $\{1\}$ , Tao Wu  $\{1\}$ , Xuming He  $\{2\}$ , Qi Sun  $\{3\}$ , Cheng Zhuo  $\{3\}$ , Bei Yu  $\{4\}$ , Jingyi Yu  $\{1\}$ , Hao Geng  $\{1\}$

{1} ShanghaiTech University, China; {2} ShanghaiTech University, China; {3} Zhejiang University, China; {4} The Chinese University of Hong Kong, Hong Kong Special Administrative Region of China

11:00

#### 589: CorDBA: Corners Decoupled Bayesian Approach for yield optimization

Yue Zhang {1}, Yunqi Li {2}, Shichang Ye {2}, Bojun Zhang {2}, Jinkai Wang {2}, Zhizhong Zhang {2}, Peng Wang {2}

{1} Beihang university, China; {2} Beihang University, China

11:15

#### 354: BAGNet: A Boundary-Aware Graph Neural Network for SRAM Yield Analysis in Post-Layout Simulation

Haoyang Sang {1}, Changhao Yan {2}, Zhaori Bi {1}, Keren Zhu {1}, Xuan Zeng {1} {1} Fudan University, China; {2} Associate Prof. Fudan University, China

#### 10:00 - 11:30

#### **Memory and Storage Design Optimization Techniques**

Room: Rome

Session Chair(s): Christian Pilato, Politecnico di Milano

Christian Haubelt, University of Rostock, Germany

This session showcases some cutting-edge system-level optimization techniques on memory and storage systems, including cache, CXL Memory, HBM, SSD, as well as near-and in-memory processing.

10:00

### 152: Rhea: a Framework for Fast Design and Validation of RTL Cache-Coherent Memory Subsystems

Davide Zoni, Andrea Galimberti, Adriano Guarisco Politecnico di Milano, Italy

10:15

### 196: LsCMM-H: A TCO-Optimized Hybrid CXL Memory Expansion Architecture with Log Structure

Xingyu Chen {1}, Xiangrui Zhang {1}, Sirui Peng {1}, Zhiwang Guo {2}, Haidong Tian {3}, Xiankui Xiong {3}, Xiaoyong Xue {1}, Xiaoyang Zeng {1}

{1} State Key Laboratory of Integrated Chips and Systems, School of Microelectronics, Fudan University, China; {2} the State Key Laboratory of Integrated Chips and Systems, School of Microelectronics, Fudan University, China; {3} State Key Laboratory of Mobile Network and Mobile Multimedia Technology, ZTE Corporation, China

10:30

### 229: STAR: Improving Lifetime and Performance of High-Capacity Modern SSDs Using State-Aware Randomizer

Omin Kwon  $\{1\}$ , Kyungjun Oh  $\{1\}$ , Jaeyong Lee  $\{1\}$ , Myungsuk Kim  $\{2\}$ , Jihong Kim  $\{1\}$   $\{1\}$  Seoul National University, Republic of Korea;  $\{2\}$  Kyungpook National University, Republic of Korea

10:45

#### 705: Addressing Thermal Throttling in HBM

Gaurav Kothari, Kanad Ghose

Dept. of Computer Science, SUNY-Binghamton, United States

11:00

#### 937: HD-MoE: Hybrid and Dynamic Parallelism for Mixture-of-Expert LLMs with 3D Near-Memory Processing

Haochen Huang  $\{1\}$ , Shuzhang Zhong  $\{1\}$ , Zhe Zhang  $\{2\}$ , Shuangchen Li  $\{3\}$ , Dimin Niu  $\{4\}$ , Hongzhong Zheng  $\{5\}$ , Runsheng Wang  $\{1\}$ , Meng Li  $\{6\}$

{1} Peking University, China; {2} Alibaba, China; {3} Tsinghua University, China; {4} Alibaba Group, United States; {5} Damo Academy & Hupan Lab, China; {6} Institute for Artificial Intelligence and School of Integrated Circuits, Peking University, China

11:15

### 1339: CIMWise: An IREE-based End-to-End AI Compiler with Auto-Tuning for CIM Processors

Bo Mai {1}, Jin Wang {1}, Zhen Zhai {1}, Liang Zhang {1}, Yufu Zhang {2}, Longyang Lin {1} {1} Southern University of Science and Technology, China; {2} Southern University of Science and Technology

10:00 - 11:30

Speeding and Learning for Achieving 2D and 3D Design Closure

Room: Barcelona

Session Chair(s): Hung-Ming Chen, National Yang Ming Chiao Tung University

Jinjun Xiong, University of Buffalo

How can we speed up the design flow in modern 2D and 3D designs? In this session, we present how we use GPU, LLM, and unified flow tweaks towards better methodologies for design closure.

#### 10:00

#### 422: GPU Acceleration for Versatile Buffer Insertion

Yuan Pu {1}, Yuhao Ji {2}, Siying Yu {3}, Zuodong Zhang {4}, Zizheng Guo {5}, Zhuolun He {1}, Yibo Lin {5}, David Z. Pan {6}, Bei Yu {1}

{1} The Chinese University of Hong Kong, Hong Kong Special Administrative Region of China; {2} Chinese University of Hong Kong, Hong Kong Special Administrative Region of China; {3} University of Illinois at Urbana-Champaign, United States; {4} School of Integrated Circuits, Peking University, China; {5} Peking University, China; {6} University of Texas at Austin, United States

#### 10:15

# 1280: BUFFALO: PPA-Configurable, LLM-based Buffer Tree Generation via Group Relative Policy Optimization

Hao-Hsiang Hsiao {1}, Yi-Chen Lu {2}, Sung Kyu Lim {3}, Haoxing Ren {4}

{1} Georgia Institute of Technology, United States; {2} Nvidia, United States; {3} Georgia Tech, United States; {4} NVIDIA Corporation, United States

#### 10:30

# 962: A Parallel Analytical Legalization Algorithm via Alternating Direction Method of Multipliers

Jaekyung Im, Seokhyeong Kang

Pohang University of Science and Technology, Republic of Korea

#### 10:45

### 1091: A Unified Design Flow for Homogeneous and Heterogeneous 3D Integration with Fine-Pitch Hybrid Bonding

Gyumin Kim {1}, Heechun Park {2}

{1} Ulsan National Institute of Science & Technology, Republic of Korea; {2} Ulsan National Institute of Science and Technology (UNIST), Republic of Korea

#### 11:00

#### 1229: Snake-3D: Differentiable Learning for Cross-Tier Logic Path Snaking Optimization in 3D ICs

Yen-Hsiang Huang {1}, Sung Kyu Lim {2}

{1} Georgia Institute of Technology, United States; {2} Georgia Tech, United States

11:15

**479: SubtreeLU: High-Performance Parallel Sparse LU Factorization for Circuit Simulation**Jiawen Cheng, Yibin Zhang, Wenjian Yu

Tsinghua University, China

10:00 - 11:30

Special Session: Agile and Open Hardware Design and Verification

Room: Atlanta

Session Chair(s): Yun (Eric) Liang, Peking University

Compared to software design, hardware design is more expensive and time-consuming. The software development flow is agile partly because software engineers can leverage a rich set of open source tools such as runtime, middleware, etc., to get projects started and iterated easily and quickly. On the hardware side, the agile and open hardware ecosystem is rising thanks to the open ISA RISC-V and other emerging open EDA and IP tools. This not only saves costs, widens the design scope of hardware, but also provides a great opportunity for hardware innovation and creativity by designing and verifying custom hardware for different needs. This special session is formulated to be as broadly interesting and useful as possible to students, researchers and faculty, and to practice engineering in both EDA and hardware design area. This session is 2 hours, consisting of five talks. The first talk presents a machine learning accelerator design as RISC-V extension using an open source flow. The second talk develops an open CGRA framework. The third talk presents an FPGA-based open source RISC-V emulation platform. The fourth talk presents an agile hardware testing framework based on reinforcement learning. The last talk introduces an open-Source ASIP design framework.

10:00

# 20034: Invited Paper: Design of Machine Learning Accelerators as RISC-V Extensions using an Open Source Tool Flow

Batuhan Sesli, Muhammad Sabih, Frank Hannig, Jürgen Teich Friedrich-Alexander-Universität Erlangen-Nürnberg (FAU), Germany

10:15

#### 20035: Invited Paper: Building an Open CGRA Ecosystem for Agile Innovation

Rohan Juneja {1}, Pranav Dangi {1}, Thilini Kaushalya Bandara {2}, Zhaoying Li {1}, Dhananjaya Wijerathne {3}, Li-Shiuan Peh {1}, Tulika Mitra {1}

{1} National University of Singapore, Singapore; {2} Renesas Electronics; {3} Advanced Micro Devices

10:30

# 20036: Invited Paper: FEMU: An FPGA-Based Open-Source RISC-V Emulation Platform for Edge Al Systems Prototyping

Simone Machetti {1}, Deniz Kasap {1}, Juan Sapriza {1}, Rubén Rodríguez Álvarez {1}, Hossein Taji {1}, José Miranda {2}, Miguel Peón-Quirós {3}, David Atienza {1}

{1} École Polytechnique Fédérale de Lausanne (EPFL), Switzerland; {2} Center of Industrial Electronics (CEI), UPM, Madrid, Spain; {3} EcoCloud, EPFL, Lausanne, Switzerland

10:45

20037: Invited Paper: CURE-Fuzz: Curiosity-Driven Reinforcement Learning for Enhanced Hardware Fuzzing in Agile Testing

Hanwei FAN {1}{2}, Ya Wang {1}, Xiaofeng Zhou {1}, Sicheng Li {3}, Binguang Zhao {3}, Yangdi Lyu {4}, Jiang Xu {4}, Wei Zhang {1}{2}

{1} Hong Kong University of Science and Technology, China; {2} Guangzhou HKUST Fok Ying Tung Research Institute; {3} Damo Academy & Hupan Lab, Alibaba, {4} The Hong Kong University of Science and Technology (Guangzhou)

11:00